# **ELECTRONIQUE NUMERIQUE**

# Partie 1 : Les systèmes combinatoires (UE Digital I)

Année académique 2023 - 2024

Titulaire:

Joël Pochet

Département technique

Section Electronique – Finalité Electronique Appliquée

Q1 bloc1

## Table des matières

| 1              | Introduction                                                                                                                       | 7        |

|----------------|------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1            | Représentations analogique et numérique d'une grandeur physique                                                                    | 7        |

| 1.2            | Les systèmes binaires                                                                                                              | 8        |

| 1.3            | Matérialisation physique d'un système binaire                                                                                      | 8        |

| 1.4            | Avantage d'un système physique binaire                                                                                             | 8        |

| 1.5            | Avantages de l'électronique (numérique et analogique)                                                                              | 8        |

| 1.6            | Brève histoire de l'électronique numérique                                                                                         | 8        |

| 1.7            | L'électronique numérique moderne. Contenu de ce cours.                                                                             | 9        |

| 1.8            | Compétences à atteindre. Comment réussir le cours théorique? Auto-évaluation.                                                      | 10       |

| 1.9            | L'électronique analogique devient de plus en plus importante!                                                                      | 11       |

| 1.10           | Apprendre à fabriquer des produits fiables, ou faire faillite                                                                      | 11       |

| 1.11           | EXERCICES (Sujets de réflexion)                                                                                                    | 12       |

| 2              | Concepts numériques de base                                                                                                        | 13       |

| 2.1            | Système binaire électronique: Association de tensions aux 2 niveaux logiques                                                       | 13       |

| 2.2            | Timing diagram = "A.C." diagram = Chronogramme = diagramme temporel                                                                | 14       |

| 2.3            | Opérations logiques de base (en algèbre binaire)                                                                                   | 15       |

| 2.4            | Circuits intégrés                                                                                                                  | 16       |

| 2.5            | Matérialisation de fonctions booléennes autrement qu'en électronique                                                               | 18       |

| 2.6            | Intérêts de l'algèbre binaire                                                                                                      | 19       |

| 2.7            | EXERCICES                                                                                                                          | 20       |

| 3              | Représentation des entiers naturels: numération de position                                                                        | 22       |

| 3.1            | Introduction                                                                                                                       | 22       |

| 3.2            | Rappel : Base 10 (numération décimale)                                                                                             | 22       |

| 3.3            | Base B quelconque                                                                                                                  | 22       |

| 3.4            | Base 2 (binaire)                                                                                                                   | 23       |

| 3.5            | Base hex (hexadécimale)                                                                                                            | 23       |

| 3.6            | Utilisation de différentes bases                                                                                                   | 23       |

| 3.7            | Conversion d'un entier naturel d'une base à une autre base                                                                         | 24       |

| 3.7.1          | Base B (par ex. Hex ou Bin) $ ightarrow$ Décimal                                                                                   | 24       |

| 3.7.2          | Base $B = 2^n$ (par ex. Hex) $\leftrightarrow$ Binaire                                                                             | 25       |

| 3.7.3<br>3.7.4 | Décimal $\rightarrow$ base B (B entier quelconque, et en particulier 16 ou 2)<br>Base hex = intermédiaire entre décimal et binaire | 26<br>27 |

| 3.7.5          | Pour information: Base B1 quelconque → autre base B2 quelconque                                                                    | 27       |

| 3.8            | EXERCICES                                                                                                                          | 28       |

| 4              | Divers codes                                                                                                                       | 29       |

| 4.1                                       | Codes. Codes binaires                                                                                                                                                                                                                                                 | 29                         |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 4.2                                       | Le codage BCD                                                                                                                                                                                                                                                         | 29                         |

| 4.3                                       | Le code Gray (code binaire réfléchi) (BRGC)                                                                                                                                                                                                                           | 30                         |

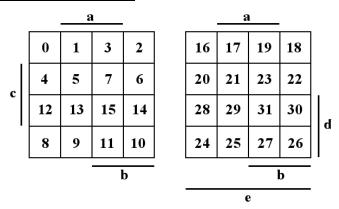

| 4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5 | Problème de la numérotation binaire naturelle<br>Définition du code Gray<br>Pour information − Distance de Hamming entre 2 suites de bits de même longueur<br>Ciruit convertisseur Binaire pur ↔ Gray.<br>Note : Numérotation des cellules dans une table de Karnaugh | 30<br>30<br>31<br>31<br>31 |

| 4.4                                       | Les codes alphanumériques. ASCII, Unicode                                                                                                                                                                                                                             | 32                         |

| 4.4.1                                     | Code ASCII en 7 bit                                                                                                                                                                                                                                                   | 33                         |

| 4.5                                       | EXERCICES                                                                                                                                                                                                                                                             | 35                         |

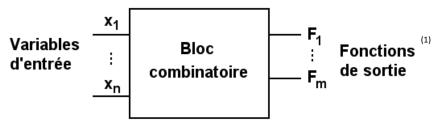

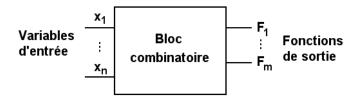

| 5                                         | Systèmes combinatoires et fonctions combinatoires de base                                                                                                                                                                                                             | 36                         |

| 5.1                                       | Systèmes combinatoires. État d'entrée. État de sortie                                                                                                                                                                                                                 | 36                         |

| 5.2                                       | Définition : système "combinatoire". Description d'un système combinatoire                                                                                                                                                                                            | 36                         |

| 5.3                                       | Fonctions combinatoires (opérateurs ou portes logiques) de base                                                                                                                                                                                                       | 37                         |

| 5.4                                       | Fonction NOT (l'inverseur)                                                                                                                                                                                                                                            | 37                         |

| 5.5                                       | Table de vérité                                                                                                                                                                                                                                                       | 38                         |

| 5.6                                       | Fonction BUFFER                                                                                                                                                                                                                                                       | 38                         |

| 5.7                                       | Dessin : Boule (bille, cercle) d'inversion                                                                                                                                                                                                                            | 39                         |

| 5.8                                       | Fonction AND                                                                                                                                                                                                                                                          | 40                         |

| 5.9                                       | Fonction OR (logical OR)                                                                                                                                                                                                                                              | 41                         |

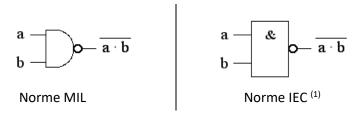

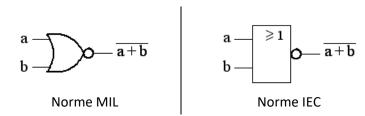

| 5.10                                      | Fonction NAND                                                                                                                                                                                                                                                         | 42                         |

| 5.11                                      | Fonction NOR                                                                                                                                                                                                                                                          | 42                         |

| 5.12                                      | EXERCICES                                                                                                                                                                                                                                                             | 43                         |

| 6                                         | Algèbre de Boole : Propriétés des opérateurs booléens NOT, AND, OR                                                                                                                                                                                                    | 44                         |

| 6.1                                       | Propriétés inspirées des opérateurs algébriques + et $\times$ pour les réels                                                                                                                                                                                          | 44                         |

| 6.2                                       | Théorème de "De Morgan"                                                                                                                                                                                                                                               | 45                         |

| 6.2.1<br>6.2.2                            | Théorème de De Morgan à 2 variables<br>Théorème de De Morgan à n variables                                                                                                                                                                                            | 45<br>46                   |

| 6.3                                       | EXERCICES                                                                                                                                                                                                                                                             | 46                         |

| 7                                         | Algèbre de Boole : Synthèse d'une fonction                                                                                                                                                                                                                            | 49                         |

| 7.1                                       | Expressions et systèmes équivalents                                                                                                                                                                                                                                   | 49                         |

| 7.2                                       | Opérateurs complets                                                                                                                                                                                                                                                   | 50                         |

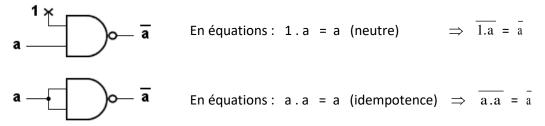

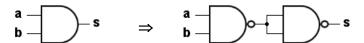

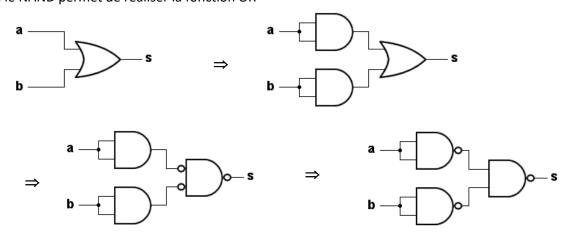

| 7.2.1<br>7.2.2<br>7.2.3                   | Ensemble d'opérateurs complet. Opérateur complet<br>Les trois opérateurs NOT, AND et OR forment un ensemble d'opérateurs complet<br>Le NAND est un opérateur complet                                                                                                  | 50<br>50<br>50             |

| 7.3                                       | Numérotation usuelle des lignes d'une table de vérité                                                                                                                                                                                                                 | 51                         |

| 7.4                                       | Monôme, polynôme. Minterm                                                                                                                                                                                                                                             | 52                         |

| 7.5                              | Exemples                                                                                                                                                                                     | 53                   |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 7.6                              | SDP standard d'une fonction combinatoire                                                                                                                                                     | 53                   |

| 7.7                              | EXERCICES                                                                                                                                                                                    | 55                   |

| 8                                | Quelques fonctions combinatoires usuelles                                                                                                                                                    | 58                   |

| 8.1                              | Signal actif haut, signal actif bas. Choix du nom d'un signal                                                                                                                                | 58                   |

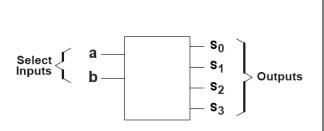

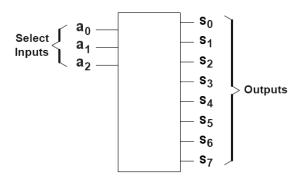

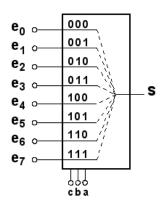

| 8.2                              | Le décodeur $n \rightarrow 2^n$                                                                                                                                                              | 59                   |

| 8.2.1<br>8.2.2                   | Définition et fonction 74xx139 (dual 2 $\rightarrow$ 4 decoder), 74xx138 (3 $\rightarrow$ 8 decoder), 74xx238 (3 $\rightarrow$ 8 decoder)                                                    | 59<br>59             |

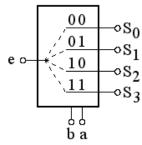

| 8.3                              | Le démultiplexeur $1 \rightarrow 2^n$                                                                                                                                                        | 60                   |

| 8.3.1                            | Définition et fonction                                                                                                                                                                       | 60                   |

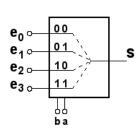

| 8.4                              | Le multiplexeur (en abrégé: le "mux")                                                                                                                                                        | 61                   |

| 8.4.1                            | Définition et fonction                                                                                                                                                                       | 61                   |

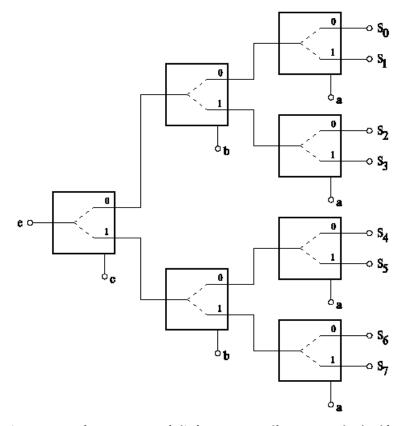

| 8.5                              | Circuits combinant plusieurs mux et/ou démux                                                                                                                                                 | 62                   |

| 8.5.1                            | Démux à grand nombre d'entrées                                                                                                                                                               | 62                   |

| 8.6                              | Utilisation d'un Mux comme "Fonction combinatoire universelle"                                                                                                                               | 62                   |

| 8.7                              | Le Théorème du consensus                                                                                                                                                                     | 63                   |

| 8.7.1<br>8.7.2<br>8.7.3          | Énoncé<br>Aléa d'une fonction logique<br>Terme de couverture                                                                                                                                 | 63<br>63<br>64       |

| 8.8                              | EXERCICES                                                                                                                                                                                    | 65                   |

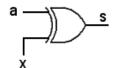

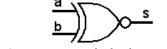

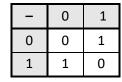

| 9                                | Fonctions XOR et XNOR                                                                                                                                                                        | 66                   |

| 9.1                              | Fonction XOR à 2 variables                                                                                                                                                                   | 66                   |

| 9.2                              | Propriétés du XOR                                                                                                                                                                            | 67                   |

| 9.2.1<br>9.2.2<br>9.2.3<br>9.2.4 | Inverseur conditionnel<br>Comparaison de non-égalité (Détecteur de différence)<br>Inversion d'une des entrées d'un XOR<br>Propriétés du XOR utiles pour des circuits de calcul arithmétiques | 67<br>67<br>67<br>68 |

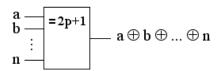

| 9.3                              | XOR à 3 entrées                                                                                                                                                                              | 69                   |

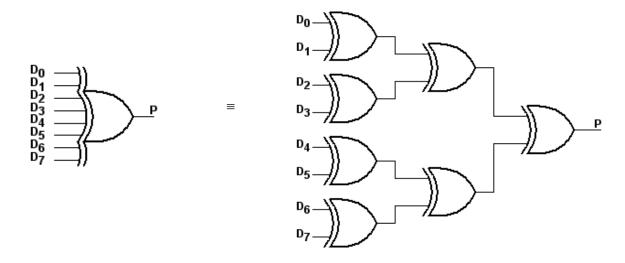

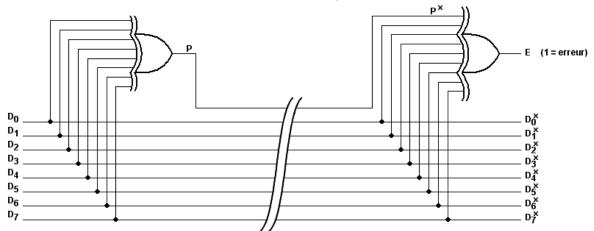

| 9.4                              | Bit de Parité et détection d'erreur                                                                                                                                                          | 69                   |

| 9.4.1<br>9.4.2                   | Application : Détection d'une erreur de transmission<br>Efficacité de la détection d'erreur au moyen d'un bit de parité.                                                                     | 71<br>71             |

| 9.5                              | Fonction XNOR                                                                                                                                                                                | 72                   |

| 9.5.1                            | Comparateur (Détecteur d'égalité) de 2 nombres binaires de n bits                                                                                                                            | 72                   |

| 9.6                              | EXERCICES                                                                                                                                                                                    | 73                   |

| 10                               | Fonction incomplètement définie                                                                                                                                                              | 74                   |

| 10.1                             | Conditions indifférentes ("don't care" conditions)                                                                                                                                           | 74                   |

| 10.2                             | Conditions impossibles ("don't happen" conditions)                                                                                                                                           | 74                   |

| 10.3                             | Remarque                                                                                                                                                                                     | 74                   |

|                                  |                                                                                                                                                                                              |                      |

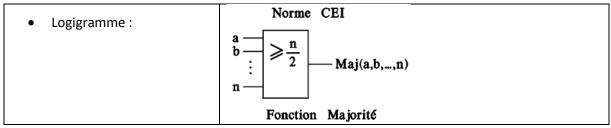

| 10.4                                 | Exemple : Fonction majorité                                                                                                                                                               | 75                   |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 10.4.1                               | Fonction majorité à 3 variables Maj (a, b, c)                                                                                                                                             | 75                   |

| 10.4.2                               | Fonction majorité à 4 variables Maj (a, b, c, d)                                                                                                                                          | 76                   |

| 10.4.3                               | Fonction majorité à 5 variables Maj (a, b, c, d, e)                                                                                                                                       | 76                   |

| 11                                   | Analyse des systèmes combinatoires                                                                                                                                                        | 77                   |

| 11.1                                 | Analyse : définition                                                                                                                                                                      | 77                   |

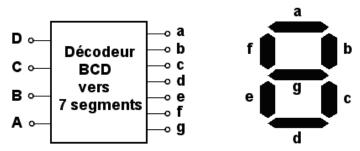

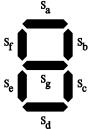

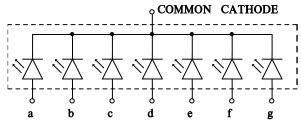

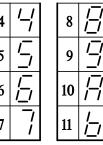

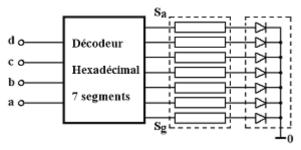

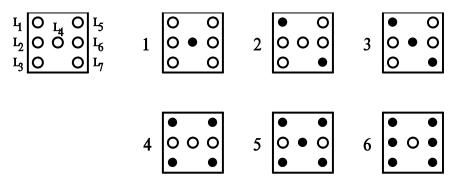

| 11.2                                 | Exemple : Décodeur hexadécimal-7segments                                                                                                                                                  | 77                   |

| 11.3                                 | EXERCICES                                                                                                                                                                                 | 79                   |

| 12                                   | Synthèse des systèmes combinatoires. Intro. : Table de Karnaugh                                                                                                                           | 81                   |

| 12.1                                 | Synthèse. Simplification. Somme minimale. Méthodes de simplification.                                                                                                                     | 81                   |

| 12.2                                 | Rappel : Disposition d'une Table de vérité                                                                                                                                                | 82                   |

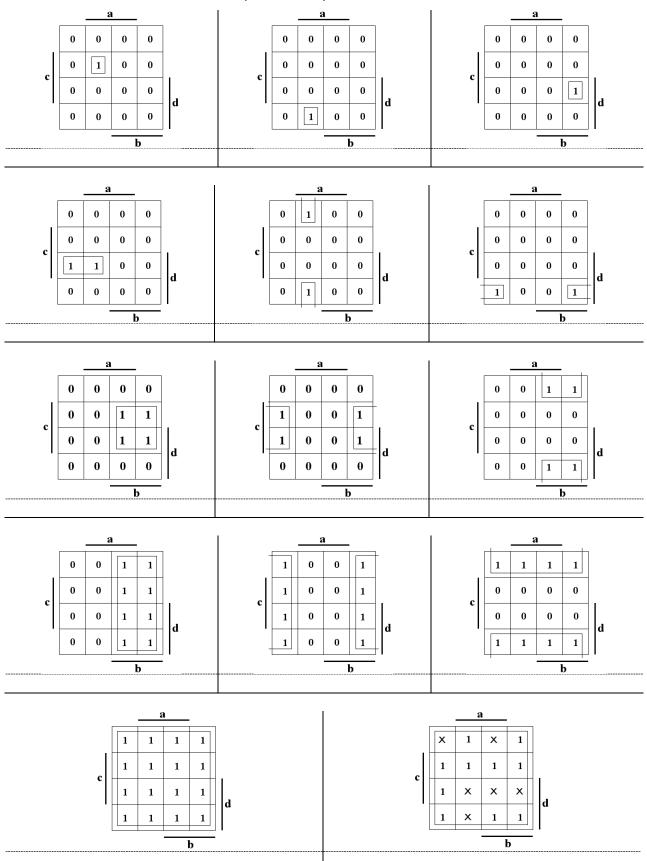

| 12.3                                 | Table de Karnaugh (= Diagramme de Karnaugh = Karnaugh-map = K-map)                                                                                                                        | 82                   |

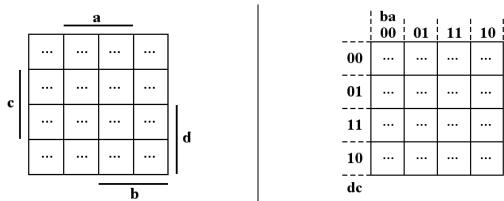

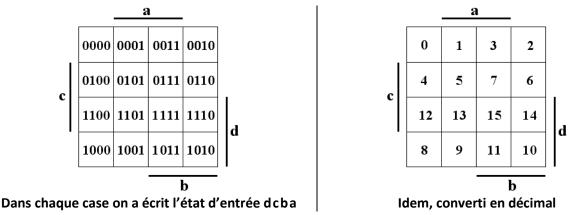

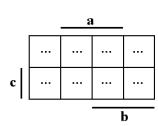

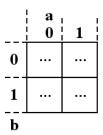

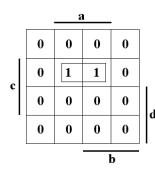

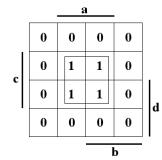

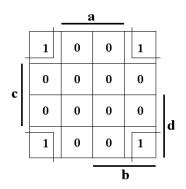

| 12.3.1<br>12.3.2<br>12.3.3<br>12.3.4 | Table de Karnaugh à 4 variables<br>Ordre des cases et remplissage de la Table de Karnaugh depuis la Table de Vérité<br>Table de Karnaugh à 3 variables<br>Table de Karnaugh à 2 variables | 82<br>83<br>84<br>85 |

| 13                                   | Synthèse : Méthode de Karnaugh                                                                                                                                                            | 86                   |

| 13.1                                 | Minterms et cases de la table de Karnaugh                                                                                                                                                 | 86                   |

| 13.2                                 | Regroupements de 2 cases contiguës en un pavé                                                                                                                                             | 86                   |

| 13.3                                 | Regroupements de 2 pavés contigus en un seul pavé                                                                                                                                         | 86                   |

| 13.4                                 | Trouver le monôme correspondant à un pavé                                                                                                                                                 | 87                   |

| 13.5                                 | Continuation des regroupements, et monômes correspondants                                                                                                                                 | 87                   |

| 13.6                                 | Les colonnes et les lignes extérieures de la Table de Karnaugh sont connexes                                                                                                              | 87                   |

| 13.7                                 | Cas des fonctions incomplètement spécifiées                                                                                                                                               | 88                   |

| 13.8                                 | Résumé de la méthode de simplification par table de Karnaugh                                                                                                                              | 88                   |

| 13.9                                 | Synthèse du complément de la fonction                                                                                                                                                     | 88                   |

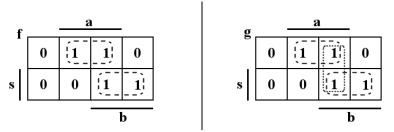

| 13.10                                | Pour information : simplification supplémentaire grâce au XOR                                                                                                                             | 88                   |

| 13.11                                | EXERCICES                                                                                                                                                                                 | 89                   |

| 14                                   | Opérations arithmétiques sur les entiers naturels exprimés en binaire                                                                                                                     | 94                   |

| 14.1                                 | Tables des 4 opérations arithmétiques sur des nombres de 1 chiffre                                                                                                                        | 94                   |

| 14.2                                 | Opérations arithmétiques sur des nombres de plusieurs chiffres                                                                                                                            | 94                   |

| 14.3                                 | EXERCICES                                                                                                                                                                                 | 95                   |

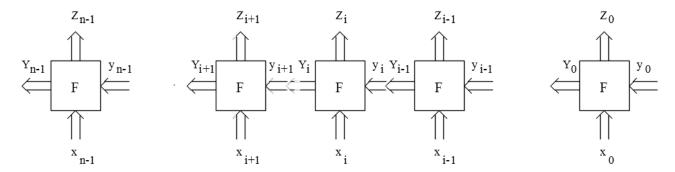

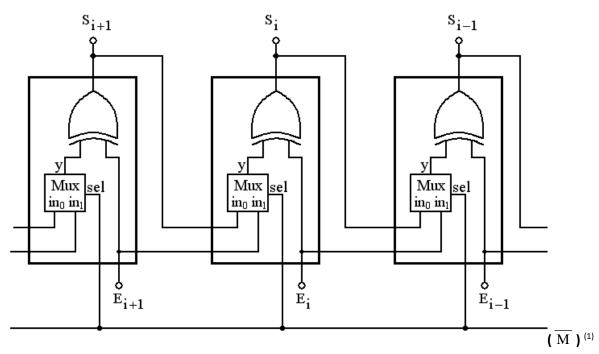

| 15                                   | Systèmes itératifs                                                                                                                                                                        | 96                   |

| 15.1                                 | Introduction                                                                                                                                                                              | 96                   |

| 15.2                                 | Définition et structure générale d'un système itératif                                                                                                                                    | 96                   |

| 15.3                                 | Avantages et inconvénients des systèmes itératifs                                                                                                                                         | 96                   |

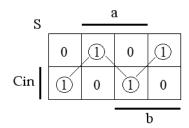

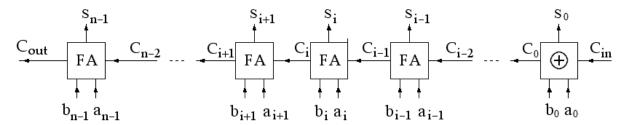

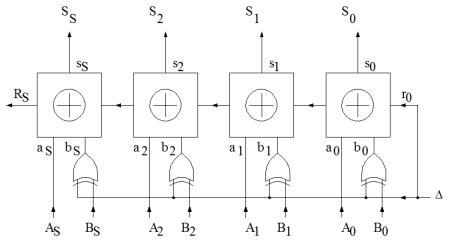

| 15.4                                           | L'additionneur binaire arithmétique (cà-d. pour des nombres $\geq 0$ )                                                                                                                                                                                                                                                                      | 96                       |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 15.4.1<br>15.4.2<br>15.4.3<br>15.4.4<br>15.4.5 | L'addition décimale  Addition binaire arithmétique (= pour des entiers naturels = positifs ou nuls)  Cellule "demi-additionneur" = additionneur sans report à l'entrée = "Half-Adder"  Cellule "Additionneur binaire avec reports (entrée et sortie)" = "1-bit Full-Adder'  Additionneur arithmétique binaire itératif (= cascade) à n bits |                          |

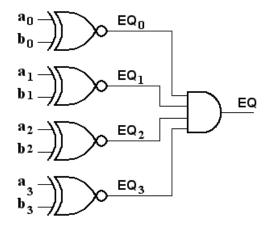

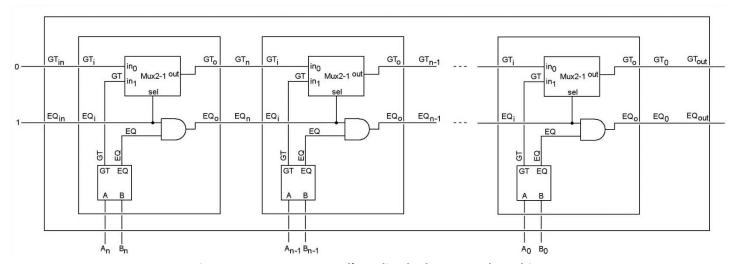

| 15.5                                           | Le comparateur (détecteur d'égalité)                                                                                                                                                                                                                                                                                                        | 102                      |

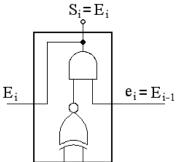

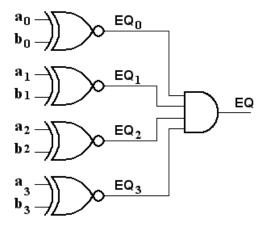

| 15.5.1<br>15.5.2<br>15.5.3<br>15.5.4           | La cellule détecteur d'égalité sans entrée report<br>La cellule détecteur d'égalité avec entrée report<br>Le comparateur (détecteur d'égalité) à n bits (structure en cascade)<br>Le comparateur (détecteur) d'égalité à n bits (structure en parallèle)                                                                                    | 102<br>103<br>104<br>104 |

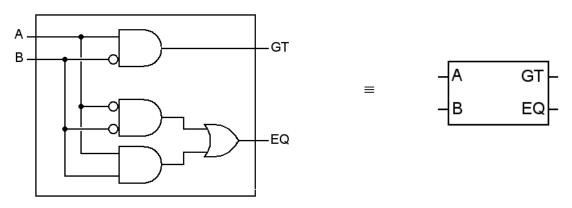

| 15.6                                           | Comparateur d'amplitude de 2 nombres binaires                                                                                                                                                                                                                                                                                               | 105                      |

| 15.6.1<br>15.6.2<br>15.6.3                     | Cellule comparateur sans entrée report<br>Cellule comparateur avec entrées de report<br>Cellule comparateur du commerce                                                                                                                                                                                                                     | 105<br>106<br>106        |

| 15.8                                           | Le soustracteur, et l'additionneur/soustracteur arithmétiques binaires                                                                                                                                                                                                                                                                      | 107                      |

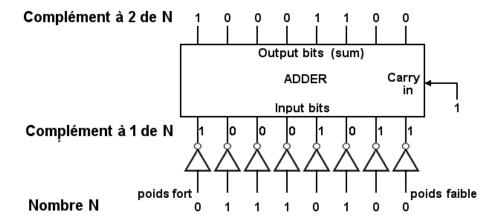

| 16                                             | Représentation des entiers positifs ET négatifs dans une machine                                                                                                                                                                                                                                                                            | 108                      |

| 16.1                                           | Représentation des entiers ≥ 0 et < 0 dans une machine décimale à 3 chiffres                                                                                                                                                                                                                                                                | 108                      |

| 16.2                                           | Représentation des entiers positifs et négatifs dans une machine binaire                                                                                                                                                                                                                                                                    | 109                      |

| 16.2.1                                         | Calcul du nombre N à partir de son code (sa représentation) K                                                                                                                                                                                                                                                                               | 110                      |

| 16.3                                           | Additionneur-soustracteur algébrique en complément à 2 ("complément vrai")                                                                                                                                                                                                                                                                  | 111                      |

| 16.4                                           | EXERCICES                                                                                                                                                                                                                                                                                                                                   | 112                      |

| 17                                             | Représentation des nombres positifs fractionnaires en base B                                                                                                                                                                                                                                                                                | 113                      |

| 17.1                                           | Représentation en base B des nombres fractionnaires $0 \le N < 1$                                                                                                                                                                                                                                                                           | 113                      |

| 17.2                                           | Conversion base 10 $\rightarrow$ base B pour des nombres fractionnaires 0 $\leq$ N $<$ 1                                                                                                                                                                                                                                                    | 114                      |

| 17.3                                           | Conversion base 10 $\rightarrow$ base B pour des nombres fractionnaires $N \ge 1$                                                                                                                                                                                                                                                           | 115                      |

| 17.4                                           | Représentation des nombres en virgule fixe                                                                                                                                                                                                                                                                                                  | 116                      |

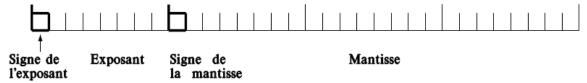

| 17.5                                           | Virgule flottante (représentation par une mantisse et un exposant)                                                                                                                                                                                                                                                                          | 117                      |

| 17.6                                           | Dynamique et précision relative                                                                                                                                                                                                                                                                                                             | 118                      |

| 17.7                                           | Implémentation : généralités                                                                                                                                                                                                                                                                                                                | 118                      |

| 17.8                                           | Implémentation standard : la norme ANSI/IEEE 754-1985                                                                                                                                                                                                                                                                                       | 120                      |

| 17.9                                           | EXERCICES                                                                                                                                                                                                                                                                                                                                   | 122                      |

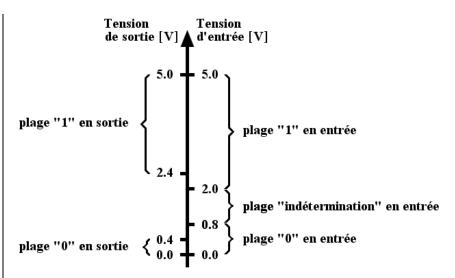

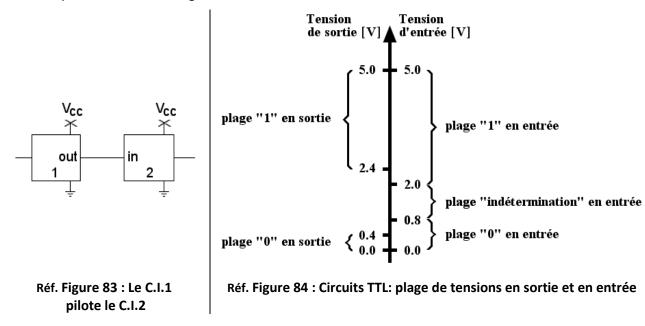

| 18                                             | Caractéristiques électriques des niveaux logiques                                                                                                                                                                                                                                                                                           | 123                      |

| 18.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                | 123                      |

| 18.2                                           | Fonctionnement au niveau haut                                                                                                                                                                                                                                                                                                               | 123                      |

| 18.3                                           | Fonctionnement au niveau bas                                                                                                                                                                                                                                                                                                                | 124                      |

| 18.4                                           | Plage (zone) d'indétermination                                                                                                                                                                                                                                                                                                              | 125                      |

| 18.5                                           | Notation sans les indices                                                                                                                                                                                                                                                                                                                   | 125                      |

| 18.6                                           | Conditions de charge – Fan-out d'un circuit TTL                                                                                                                                                                                                                                                                                             | 125                      |

| © D. Ge                                        | elbgras, G. Van Vinckenroy, J. Pochet 1EA_Num1_v3.2.pdf 27 Août 2023                                                                                                                                                                                                                                                                        | pg. 5/148                |

| 18.7                          | Notion de marge dans la vie courante                                                                     | 126               |

|-------------------------------|----------------------------------------------------------------------------------------------------------|-------------------|

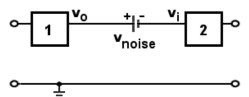

| 18.8                          | Marge de bruit (Immunité au bruit) au niveau haut                                                        | 126               |

| 18.9                          | Marge de bruit (Immunité au bruit) au niveau bas                                                         | 127               |

| 18.9.1                        | Immunité au niveau haut, immunité au niveau bas                                                          | 128               |

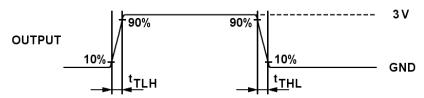

| 18.10                         | Signaux dynamiques: durée du passage dans la zone d'indétermination                                      | 129               |

| 18.10.1<br>18.10.2<br>18.10.3 | Durée maximum garantie d'un flanc en sortie (guaranteed output transition time)                          | 129<br>129<br>129 |

| 18.11                         | EXERCICES                                                                                                | 130               |

| 19                            | Annexe : fonctions logiques élémentaires en DTL et RTL                                                   | 131               |

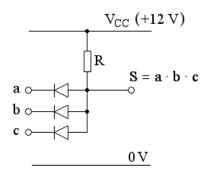

| 19.1                          | Réalisation de la fonction AND                                                                           | 131               |

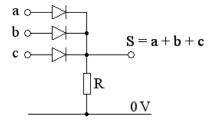

| 19.2                          | Réalisation de la fonction OR                                                                            | 131               |

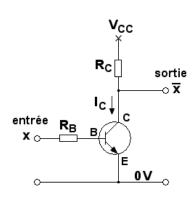

| 19.3                          | Réalisation de la fonction NOT ( = "non" = inversion ) en RTL                                            | 132               |

| 19.4                          | Réalisation de la fonction NOR en DTL                                                                    | 133               |

| 20                            | Access Additional de Manageria Committee de                                                              | 424               |

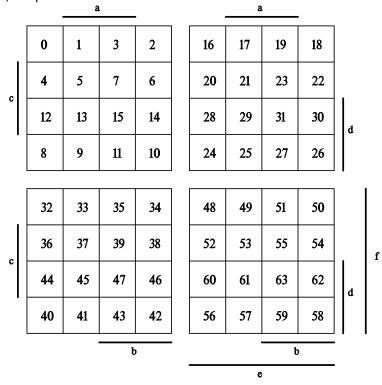

| 20                            | Annexe : Méthode de Karnaugh - Compléments                                                               |                   |

| 20.1.1<br>20.1.2              | Table de Karnaugh à 5 variables et plus<br>Note : autres numérotations des cases d'une Table de Karnaugh | 134<br>135        |

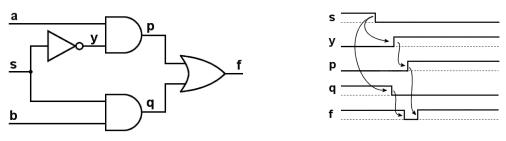

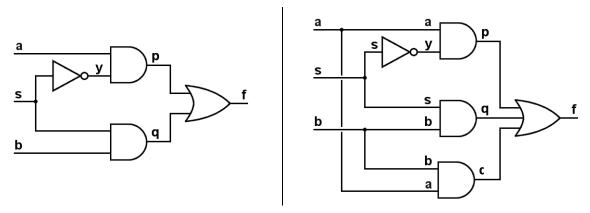

| 20.1.3                        | Couverture des aléas d'une fonction combinatoire                                                         | 135               |

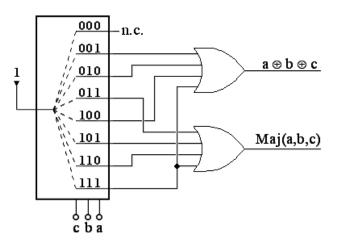

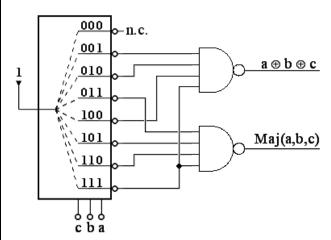

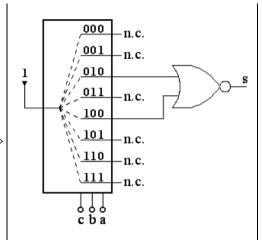

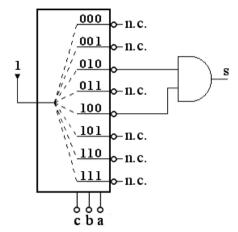

| 21                            | Annexe : Réalisation d'une fonction par mux ou démux                                                     | 136               |

| 21.1                          | Réalisation par mux                                                                                      | 136               |

| 21.2                          | Réalisation par démux, et une porte (OR, NAND, NOR, NAND)                                                | 136               |

|                               |                                                                                                          |                   |

| 22                            | Annexe: PDS standard d'une fonction combinatoire                                                         |                   |

| 22.1                          | PDS standard d'une fonction combinatoire                                                                 | 138               |

| 23                            | Annexe : Fonctions min et max d'une fonction incomplètement spécifiée                                    | 139               |

| 24                            | Annexe : équations des sorties des décodeurs, démux et mux                                               | 140               |

|                               |                                                                                                          |                   |

| 25                            | Annexe : Synthèse par simplification algébrique "libre"                                                  | 141               |

| 26                            | Annexe : Codeur/décodeur Binaire pur ↔ Gray                                                              | 142               |

| 26                            |                                                                                                          |                   |

| <b>26</b><br>26.1             | Circuit Codeur-Décodeur Binaire naturel ↔ Gray                                                           | 143               |

|                               | Circuit Codeur-Décodeur Binaire naturel ↔ Gray  Annexe : Code ASCII étendu (8 bits)                      |                   |

| 26.1                          |                                                                                                          | 145               |

#### 1 Introduction

- On peut diviser les circuits électroniques en 2 grandes catégories : analogiques et numériques

- Les entrées et les sorties des circuits analogiques sont des quantités (en général des tensions) à valeurs continues,

- Les entrées et les sorties des circuits numériques ("digitaux") sont des quantités à valeurs discrètes (c.-à-d. distinctes).

#### 1.1 Représentations analogique et numérique d'une grandeur physique

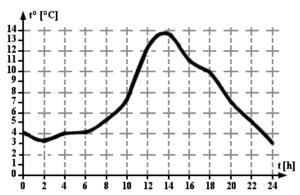

Figure 1: La t° est une grandeur analogique

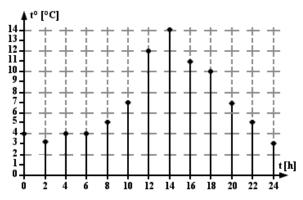

Figure 2: Numérisation de la t°

- On peut représenter la valeur d'une grandeur physique (par ex. la température) de 2 façons :

- Représentation analogique :

par un nombre réel = variant d'une façon continue.

Exemple **Figure 1**:

la t° peut prendre n'importe quelle valeur: sa variation est **continue**.

Représentation numérique = digitale (1):

par un nombre (généralement entier) pouvant prendre seulement des valeurs "discrètes" = variant de façon discontinue = par sauts.

Exemple **Figure 2** : un thermomètre à affichage numérique représente la t° par un nombre variant par exemple par pas de 1 °C : le plus petit saut est 1 °C.

- Un système analogique peut sembler plus précis, puisqu'il peut représenter un nombre infini de valeurs. Mais, sauf à la t° absolue non atteignable de 0 K, un bruit de fond aléatoire s'ajoute de façon inévitable à tout signal : ce bruit limite la résolution de tout signal.

- Et un système numérique peut être tout aussi précis qu'un système analogique : même si cela en augmente le coût, on peut diminuer le pas ⇒ augmenter (2) la résolution (avec la même limitation : augmenter la résolution à une valeur inférieure au bruit n'apporte plus d'information).

Exemple : un thermomètre numérique pourrait utiliser un pas de 0,001°C : l'unité serait le millième de degré.

\_

<sup>(1)</sup> Du mot anglais "digit" : chiffre

<sup>(2)</sup> Ici augmenter la résolution signifie améliorer la résolution. Par exemple, en passant de 0,01 °C à 0,001 °C, on améliore la résolution.

#### 1.2 Les systèmes binaires

Un cas particulier (extrême) de grandeur numérique est la grandeur binaire :

Une variable binaire = une variable logique = un "bit" d'information (1) peut prendre seulement 2 valeurs (= 2 états), souvent notées "FALSE" et "TRUE", "OFF" et "ON", "LOW" (BAS) et "HIGH" (HAUT), ou "0" et "1".

#### 1.3 Matérialisation physique d'un système binaire

- Une variable binaire est un concept mathématique (abstrait). Matérialiser une variable binaire consiste à construire un système physique (concret) dans lequel une certaine grandeur physique peut prendre de façon stable seulement 2 états bien distincts.

- Cette grandeur physique peut être mécanique, pneumatique, optique, électrique,...

- En logique pneumatique, la grandeur est la pression de l'air dans un tuyau ⇒ on s'arrange pour que la pression soit

- ou bien très basse,

- ou bien très élevée.

- En électronique numérique, la grandeur est la tension (en anglais : voltage). La tension est certes une grandeur analogique, mais les circuits sont conçus afin que leur tension de sortie se stabilise rapidement, et seulement :

- soit au niveau BAS (LOW) = une valeur proche de 0 V

- soit au niveau HAUT (HIGH) = une valeur proche de la tension d'alimentation.

#### 1.4 Avantage d'un système physique binaire

- Se limiter volontairement à seulement 2 valeurs analogiques très différentes (donc faciles à créer, et à distinguer lorsqu'on mesure) offre un avantage énorme: le système a une grande immunité au bruit : même en présence de parasites, le risque est faible de mal interpréter la valeur d'un niveau (c.-à-d. de prendre un 0 pour un 1, ou inversement).

- Une grande immunité au bruit augmente énormément la fiabilité : il devient possible de

- o garantir la fidélité *parfaite* (!) d'une copie

- o stocker cette copie de façon fiable, pendant longtemps

- o construire des systèmes qu'on peut étendre (par répétition et hiérarchisation) jusqu'à de très grandes tailles

Osons le dire : tout ceci est impossible en analogique.

#### Avantages de l'électronique (numérique et analogique)

Les technologies actuelles de fabrication permettent de miniaturiser, produire en masse, et diminuer les coûts de fabrication. Des progrès en termes d'écologie sont en cours.

#### Brève histoire de l'électronique numérique 1.6

Voir <u>29 Annexe</u>

<sup>(1)</sup> De l'anglais "binary digit", chiffre binaire

#### 1.7 L'électronique numérique moderne. Contenu de ce cours.

- Les transistors permettent de fabriquer des **portes logiques** qui réalisent électriquement les opérations fondamentales de la logique binaire (booléenne) : AND, OR, NOT et de l'arithmétique : l'addition et la soustraction

- Assembler des portes AND, OR, NOT nous conduit à la logique combinatoire.

Elle permet la réalisation de codeurs, décodeurs, multiplexeurs, démultiplexeurs, ...

et par répétition de circuits simples, elle permet de créer des circuits "itératifs"

comme les circuits de calcul arithmétique (additionneurs, soustracteurs, multiplieurs...)

- En ajoutant des rétroactions, nous entrons dans la logique séquentielle.

Elle permet la réalisation de registres (mémoires), de compteurs, et d'automates variés.

- Combiner des circuits combinatoires et séquentiels nous permet de réaliser des réseaux logiques (GAL, PLD) programmables par les utilisateurs, et des microprocesseurs.

- ⇒ Tout au long de l'année, nous étudierons ces différents thèmes (avec exercices et laboratoires).

Le dernier exercice de l'année (qui occupera plusieurs séances d'exercices au cours de théorie, et plusieurs séances de laboratoire) consiste en la conception du cœur d'un microordinateur.

- ⇒ En 2<sup>ème</sup> vous apprendrez le langage VHDL<sup>(1)</sup> qui permet de créer des circuits hiérarchisés et itératifs de grande taille et très complexes, circuits qu'on matérialise par exemple dans des FPGA<sup>(2)</sup>.

<sup>(1)</sup> Very high speed integrated circuit Hardware Description Language : Language de description du matériel pour les circuits intégrés très rapides.

<sup>(2)</sup> Field Programmable Gate Array : Tableau de portes logiques, réseau logique (de grande taille) programmable par l'utilisateur.

#### 1.8 Compétences à atteindre. Comment réussir le cours théorique? Auto-évaluation.

- L'examen théorique contient seulement des exercices! Ils sont directement inspirés des exercices donnés dans le présent syllabus, pour chaque chapitre :

- Faites et refaites ces exercices:

- Comme en sport, un seul long entraînement avec beaucoup d'exercices est pénible et ... inutile.

- Faites plutôt régulièrement 1 ou 2 exercices, le plus vite possible Ceci est particulièrement vrai pour s'entraîner aux nombres hexadécimaux.

- Le livre "Systèmes numériques" de FLOYD (voir bibliographie) est disponible en prêt à la bibliothèque et contient aussi de nombreux exercices, certains corrigés.

- Vérifiez et discutez vos résultats avec vos condisciples, et vos professeurs

- Faites-vous expliquer la matière par un condisciple

- Expliquez la matière à un condisciple; inventez un exercice pour lui!

Tous les professeurs vous le diront : donner cours, se forcer à expliquer le plus clairement possible ... fait qu'on comprend mieux soi-même!

- **Vous auto-évaluer** est facile: si vous comprenez et savez résoudre les exercices du présent syllabus, si vous savez inventer des exercices semblables et les résoudre, vous réussirez.

#### 1.9 L'électronique analogique devient de plus en plus importante !

- L'expansion des technologies numériques, des microprocesseurs et de l'informatique a été spectaculaire dans les 30 dernières années, et le sera encore dans un futur proche.

- Mais alors, l'électronique analogique est-elle dépassée, obsolète?

Non, au contraire! Mais l'électronique analogique se spécialise :

- Dans la conception de circuits numériques de base de plus en plus rapides, et de plus en plus économes en énergie.

- Dans les interfaces entre les ordinateurs et le monde physique : prise de signaux, amplification de ces signaux avant mesure.

- Dans les circuits de puissance (gestion de l'énergie):

collecte d'énergies renouvelables, alimentation des ordinateurs,

contrôle de moteurs, éclairage : leur efficacité pourrait influencer le climat futur.

#### 1.10 Apprendre à fabriquer des produits fiables, ou faire faillite

Un ordinateur grand public coûtant moins de 500 € peut par exemple exécuter environ

1 milliard (10<sup>9</sup>) d'opérations par seconde : mille millions d'opérations en 1 seconde !

Or, du point de vue du fabricant de l'ordinateur, celui-ci ne fonctionne *de façon économique* que si *tous ses circuits* — en réalité analogiques — se stabilisent en des points de fonctionnement particuliers,

- o et ceci pour des millions (10<sup>6</sup>) de circuits,

- o pour des centaines de milliers (10<sup>5</sup>) d'ordinateurs,

- o et chacun pendant quelques milliers (10<sup>3</sup>) d'heures ... :

$10^9 \times 10^6 \times 10^5 \times 10^3 = 10^{23}$  ... un nombre énorme !  $\Rightarrow$  c'est seulement lorsque les circuits analogiques fonctionnent de façon *vraiment* fiable qu'on peut oublier leur fonctionnement, pour se consacrer aux problèmes numériques.

- De même, c'est seulement lorsque les circuits numériques fonctionnent de façon fiable, qu'on peut oublier leur fonctionnement pour se consacrer à l'informatique!

- Il restera alors à écrire des programmes informatiques fiables ...

## 1.11 EXERCICES (Sujets de réflexion)

| (  | Ce chapitre d'introduction a pour but de situer le sujet, et de vous donner quelques clés pour réussir. Comme nous n'avons vu quasi aucune matière, dans ce chapitre les exercices sont remplacés par quelques sujets de réflexion : |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Discutez les conséquences sociales, économiques, légales d'une technologie qui permet de faire des copies parfaites                                                                                                                  |

| 2. | Discutez les conséquences sociales, économiques, légales d'une technologie qui permet de stocker des données pendant de très longues durées                                                                                          |

| 3. | Y a-t-il des limites pratiques au stockage de données de longue durée ?                                                                                                                                                              |

| 4. | Connaissez-vous des systèmes numériques de très petite taille (miniatures, microscopiques) ?                                                                                                                                         |

| 5. | Connaissez-vous des systèmes numériques de très grande taille ?                                                                                                                                                                      |

| 6. | Discutez les conséquences sociales et économiques de ces systèmes.                                                                                                                                                                   |

| 7. | Discutez le degré de fiabilité requis pour divers produits grand public, et pour des installations industrielles.                                                                                                                    |

|    |                                                                                                                                                                                                                                      |

#### 2 Concepts numériques de base

#### 2.1 Système binaire électronique: Association de tensions aux 2 niveaux logiques

En électronique numérique, la grandeur physique utilisée qui représente une variable binaire est généralement la  $\underline{\text{tension}}^{(1)}$ :

- En logique positive (2):

- à la valeur "0", on associe une tension V<sub>L</sub> assez basse (LOW): typiquement V<sub>I</sub> = 0 V.

- $\circ$  à la valeur "1", on associe une tension V<sub>H</sub> assez haute (HIGH), typiquement V<sub>H</sub> = V<sub>CC</sub> = tension d'alimentation positive, par ex. +3,3V, +5V, +12V

avec V<sub>L</sub> << V<sub>H</sub>

- Écrire  $V_L = 0 V$  et  $V_H = V_{CC}$  est un raccourci : en réalité on utilise des *plages* de tension :

- o à la valeur "0", on associe une plage de tensions basses (proche de 0V)

- o à la valeur "1", on associe une plage de tensions élevées (proches de V<sub>CC</sub>)

- D'une famille de composants à une autre, les valeurs de ces tensions sont différentes.

Elles sont définies dans la "datasheet" du composant, publiée par son fabricant (3)

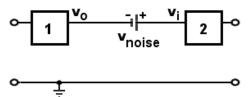

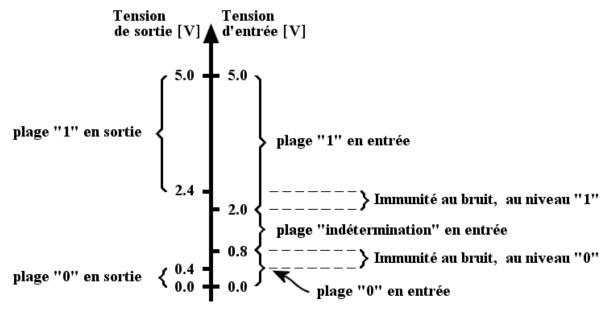

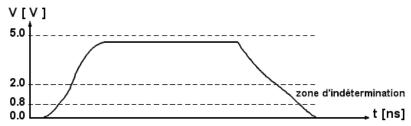

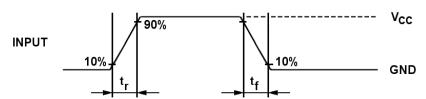

Figure 3 : Circuit TTL : plages de tension associées aux niveaux logiques 0 et 1

Cette explication est simplifiée : pour comprendre les datasheets et faire fonctionner les circuits, lisez : Chapitre 0 Caractéristiques électriques des niveaux logiques

Dans ce cours, on utiliser la logique positive, qui est plus répandue.

<sup>(1)</sup> Voir cours d'électricité et d'électronique analogique. Plus exactement, on parle ici de la tension = la différence de potentiel (aussi appelée ddp) entre le point considéré et un autre point du circuit appelé OV ou GND (zéro volt, zéro volt logique, masse, ground).

<sup>(2)</sup> En logique négative, on effectue l'association inverse :

o À la valeur "0" on associe une tension élevée,

o À la valeur "1" on associe une tension basse.

<sup>(3)</sup> On peut télécharger une datasheet depuis un site très utile comme <u>www.alldatasheet.com</u>, mais il est préférable de la télécharger depuis le site internet du fabricant du composant, afin de toujours utiliser la dernière mise à jour!

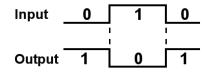

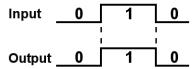

#### 2.2 <u>Timing diagram = "A.C." diagram = Chronogramme = diagramme</u> temporel

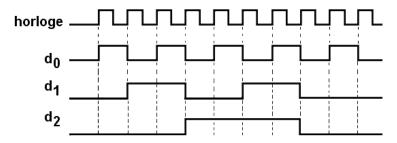

• On illustre souvent le fonctionnement d'un système numérique avec un "diagramme temporel", ou "chronogramme", qui montre l'évolution des signaux au cours du temps.

Figure 4 : Exemple de chronogramme d'un circuit numérique (compteur)

Axe horizontal : le temps

- Un chronogramme est donc ce qu'on verrait sur un oscilloscope à plusieurs traces, mais on simplifie (on idéalise) le dessin :

- O Dans un dessin simple, on ne garde que 2 niveaux de tension L et H (0 et 1)

- O Dans un dessin plus détaillé, on représente la transition d'un signal  $(L \rightarrow H, ou H \rightarrow L)$  par une ligne oblique

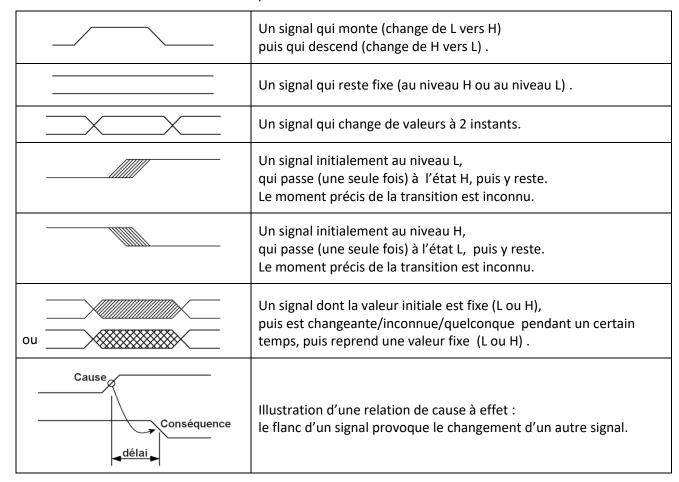

- Voici quelques conventions de dessin, utilisées par exemple dans les datasheets de microprocesseurs :

Figure 5 : Conventions de dessin utilisées dans les chronogrammes

#### 2.3 Opérations logiques de base (en algèbre binaire)

- L'algèbre binaire (1) permet d'écrire des énoncés logiques sous forme d'équations. Une équation logique correspond à l'information d'égalité entre deux expressions logiques. Une expression logique :

- o combine des variables booléennes

- o au moyen d'opérateurs (un opérateur réalise une certaine fonction logique)

- On peut traduire une équation en schéma (et un schéma en équation) :

- o chaque variable binaire est représentée par la tension d'un signal électrique

- o chaque opérateur (= fonction logique) est représenté par un symbole.

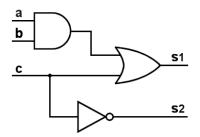

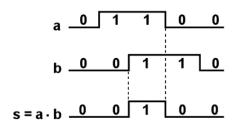

- Exemple :

$$s1(a,b,c) = s1 = (a \text{ AND } b) \text{ OR } c$$

$s2(c) = s2 = \text{ NOT } c$

Deux équations logiques a, b, et c sont les variables (binaires) s1 et s2 sont les fonctions <sup>(2)</sup> (binaires) AND, OR, NOT sont les opérateurs

Schéma a, b, et c sont les signaux d'entrée s1 et s2 sont les signaux de sortie

Symboles des opérateurs : voir **Tableau 1** : **Opérateurs logiques de base**

Figure 6: Deux équations logiques, et le schéma correspondant à ces équations

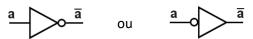

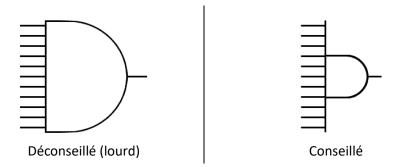

| Symbole                    | Opérateur<br>(Fonction) | Équation<br>booléenne | Commentaire                                                                                            |

|----------------------------|-------------------------|-----------------------|--------------------------------------------------------------------------------------------------------|

| a s<br>ou<br>a s           | Inverter<br>(NOT)       | s = a                 | Fonction Inverseur :<br>Si l'entrée = 0, la sortie = 1<br>Si l'entrée = 1, la sortie = 0 .             |

| <u>a</u> <u>b</u> <u>s</u> | AND                     | s = a·b               | Fonction ET :<br>La sortie vaut 1<br>si l'entrée a <b>et</b> l'entrée b valent 1                       |

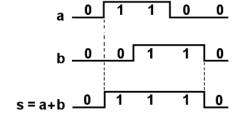

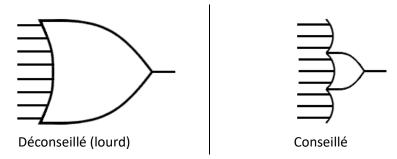

| <u>a</u> <u>b</u> s        | OR                      | s = a+b               | Fonction OR:<br>La sortie vaut 1<br>si l'entrée a vaut 1, <b>ou</b> l'entrée b vaut 1<br>(ou les deux) |

Tableau 1: Opérateurs logiques de base

- Notation : a/ ou a désigne l'inverse de a, aussi appelé : le "complément" de a

- La variable a étant binaire, on a évidemment :  $\overline{a} = a$ .

(1) ou algèbre booléenne (Boole, mathématicien irlandais, <a href="http://en.wikipedia.org/wiki/George Boole">http://en.wikipedia.org/wiki/George Boole</a>)

<sup>(2)</sup> La fonction est définie par son expression logique mais est aussi fréquemment utilisée pour identifier la variable binaire dépendante. L'utilisation du même identifiant pour la variable et le nom de la fonction apporte une facilité.

<sup>©</sup> D. Gelbgras, G. Van Vinckenroy, J. Pochet 1EA\_Num1\_v3.2.pdf 27 Août 2023

#### 2.4 <u>Circuits intégrés</u>

- Des *circuits intégrés* matérialisent les opérateurs NOT, AND, OR et d'autres fonctions logiques : en les soudant sur un PCB (Printed Circuit Board, circuit imprimé), on construit physiquement le système numérique.

- Un Circuit Intégré (C.I.) est un circuit électronique encapsulé dans un seul boîtier, (et d'habitude construit sur une seule « puce » , d'habitude de silicium).

- Cette « puce » est montée à l'intérieur du boîtier qui est en plastique ou céramique. Le boîtier protège la puce des chocs, de l'humidité et de l'oxydation.

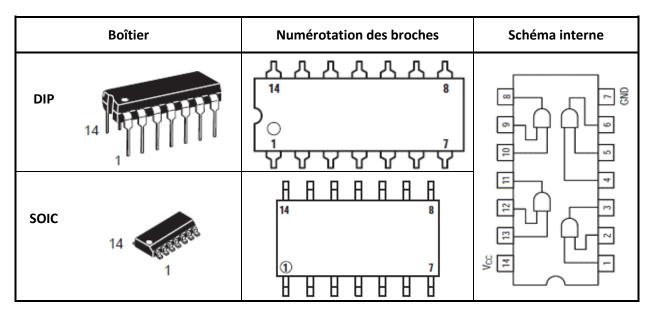

Il existe de nombreuses variantes de boîtiers. On distingue notamment :

- Boîtier DIL = DIP (Dual In-Line Package): les broches du C.I. sont du type « pin through hole »: ces broches traversent le PCB

- Boîtier SMD (Surface Mount Device) = Composant à Montage en Surface (CMS): les broches sont courbées, elles ne traversent pas le circuit imprimé. Les boîtiers SMD modernes sont très compacts, et de plus en plus utilisés, et plus difficiles à souder car les pattes sont très rapprochées.

- Exemple : le C.I. 7408 (Quadruple AND) .

Ce circuit existe en divers boîtiers, dont les deux ci-dessous :

Tableau 2: La puce du 7408 est vendue dans 2 boîtiers

Le boîtier SOIC (Small Outline Integrated Circuit) est un exemple de boîtier SMD

• On fabrique des C.I. de taille et de complexité très différentes :

| Scale Integration Nombre de portes logiques sur une même puce |           | Exemples                                                |  |

|---------------------------------------------------------------|-----------|---------------------------------------------------------|--|

| SSI (Small) jusque 10                                         |           | Portes logiques de base, bascules                       |  |

| MSI (Medium) jusque 100                                       |           | Fonctions logiques : codeurs, décodeurs, multiplexeurs, |  |

| LSI (Large) jusque 1000                                       |           | Mémoires,                                               |  |

| VLSI (Very Large) jusque 100000                               |           | Mémoires,                                               |  |

| ULSI (Ultra Large)                                            | > 100 000 | Mémoires, microprocesseurs,                             |  |

Tableau 3 : Classement des C.I. par complexité

Exemple: le C.I. 7408 (Quadruple AND) est un circuit SSI.

- On fabrique des C.I.

- o avec différents types de transistors (transistor bipolaire, transistor MOSFET),

- o avec différents matériaux semi-conducteurs (silicium, arséniure de gallium, ...)

- o nutilise ces transistors de différentes façons (en saturation, ou non)

Les choix de fabrication influencent le coût, la consommation, et la vitesse des C.I. (voir cours d'électronique analogique).

Vous utiliserez surtout des circuits du type TTL ou CMOS :

| Туре | Technologie<br>des transistors | Indications                                                   |  |  |

|------|--------------------------------|---------------------------------------------------------------|--|--|

| TTL  | bipolaire                      | SSI, MSI.                                                     |  |  |

|      |                                | Robustes. Survivent assez bien aux décharges électrostatiques |  |  |

| CMOS | MOSFET                         | Plus compacts, consomment moins d'énergie.                    |  |  |

|      |                                | Pour tous circuits (SSI jusqu'ULSI).                          |  |  |

|      |                                | Assez fragiles (notamment en cas de décharge électrostatique) |  |  |

Tableau 4: Principales technologies de C.I.

Exemple: le 7408 existe en TTL (7408, 74LS08) et en CMOS (74HC08, 74LVC08,...)

- On distingue 2 grands types de C.I. :

- o C.I. à fonction *fixe* : ses fonctions logiques sont figées, impossible à modifier.

- o C.I. à fonction *programmable*.

Exemple : le 7408 est un circuit à fonction fixe. Les PAL, les FPGA sont programmables.

• Voir aussi "Systèmes numériques", Thomas L FLOYD, 9ème édition, pg. 151 et "Le technicien en électronique", C. Cimelli, R. Bourgeron, pg. 273.

#### 2.5 Matérialisation de fonctions booléennes autrement qu'en électronique

- Nous matérialiserons les circuits logiques par des C.I., mais d'autres possibilités existent:

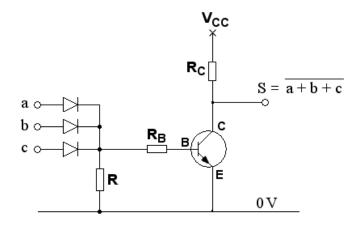

- Circuits électroniques à composants discrets : DTL et RTL (Diode Transistor Logic, Resistor Transistor Logic) qui utilisent des résistances et des diodes, et des transistors comme amplificateurs / inverseurs (voir 19 : Annexe : fonctions logiques élémentaires en DTL et RTL et le cours d'électronique analogique).

- o Circuits électriques à interrupteurs et relais, avec des lampes pour affichage

- Circuits pneumatiques

- Circuits optiques

- 0

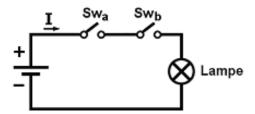

- Exemple : circuit électrique matérialisant la fonction logique "AND à 2 entrées" :

- o La sortie s du circuit vaut 1 si l'entrée a ET l'entrée b valent 1; sinon s = 0. On résume la description de la fonction s(a,b) en une "Table de Vérité" (1):

| Entrées |   | Sortie  |  |

|---------|---|---------|--|

| b       | а | s = a.b |  |

| 0       | 0 | 0       |  |

| 0       | 1 | 0       |  |

| 1       | 0 | 0       |  |

| 1       | 1 | 1       |  |

Tableau 5: Table de vérité de la fonction AND

- o s est matérialisée par une lampe : 1 = lampe allumée, 0 = lampe éteinte

- o La variable d'entrée a est matérialisée par le switch (interrupteur) Swa, la variable d'entrée b est matérialisée par Sw<sub>h</sub>. Un switch fermé représente l'état 1, un switch ouvert représente l'état 0.

Figure 7 : Un circuit électrique qui matérialise la fonction ET Ici, les 2 switches sont représentés ouverts (état 0)

Si [Sw<sub>a</sub> est fermé (état 1)] ET [Sw<sub>b</sub> est fermé (état 1)] alors [la lampe est allumée (état 1)]

© D. Gelbgras, G. Van Vinckenroy, J. Pochet 1EA\_Num1\_v3.2.pdf 27 Août 2023

<sup>(1)</sup> La sortie est une fonction des variables d'entrée. La table de vérité d'une fonction booléenne spécifie la valeur de la fonction, pour chacune des combinaisons possibles des variables

#### 2.6 Intérêts de l'algèbre binaire

Nous avons vu que l'algèbre binaire permet de représenter les relations entre les entrées et la sortie (ou les sorties) d'un circuit logique sous une forme mathématique : équation(s), ou table(s) de vérité.

Ceci offre plusieurs avantages:

- La représentation mathématique (équation(s) ou table(s))

est indépendante de la technologie qui sera choisie pour réaliser la fonction

- Dans le cas d'une fonction d'un nombre limité de variables (1) d'entrée;

l'être humain est capable (en exploitant quelques propriétés mathématiques)

de simplifier la fonction au maximum, avant de la réaliser de façon concrète

- Dans le cas d'une fonction de nombreuses variables,

il est possible de simplifier la fonction à l'aide de programmes informatiques.

- Toutefois, l'utilisation de variables binaires qui n'ont que deux valeurs possibles rallonge les expressions, qui deviennent rapidement illisibles pour l'être humain.

Aussi, avant de passer au **Chapitre 5 Systèmes combinatoires et fonctions combinatoires de base**, nous allons introduire des notations plus compactes que le binaire.

C'est l'objet du **Chapitre 3 Représentation des entiers naturels: numération de position :** nous y verrons notamment le code hexadécimal :

- o écrire des nombres en hexadécimal est beaucoup plus court qu'en binaire,

- o la conversion binaire  $\rightarrow$  hexadécimal, et la conversion hexadécimal  $\rightarrow$  binaire sont très simples.

et c'est aussi l'objet du Chapitre 4 Divers codes .

<sup>(1)</sup> Disons: 4 ou 5 variables

#### 2.7 **EXERCICES**

8. <u>Énoncé</u> : Dessinez le circuit électrique (avec des interrupteurs et une lampe) réalisant la fonction "OR à 2 entrées"

9. Dessinez les circuits d'interrupteurs correspondant aux calculs logiques suivants :

$$\circ$$

s = (a + b).c

$$\circ$$

s = [(a + b).c] + d

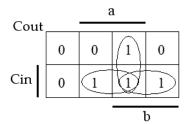

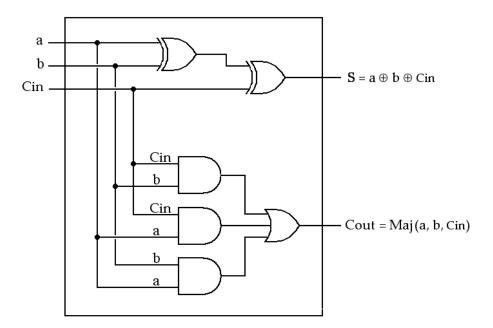

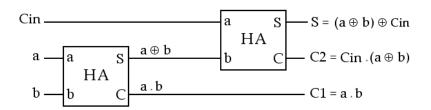

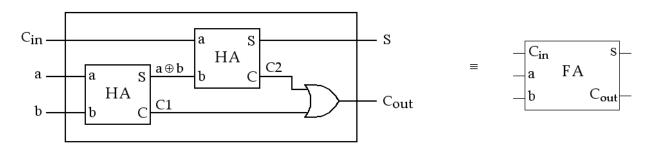

$$\circ$$